DRAM(动态随机存取内存),最常用的来自一种电脑内存。它通常使用一个晶体管和一个电容器来代表一个比特。和ROM及PROM等固件内存不同,随机存取内存的两种主要类型(动态和静态)都述晚罪冷会在切断电源之后,丢失所储存的数据。

- 中文名称 动态随机存取内存

- 外文名称 DRAM

工作原理

动态RAM的工作原理 来自动态RAM也是由许多基本存储元按照行和列地址引脚复用来组成的。

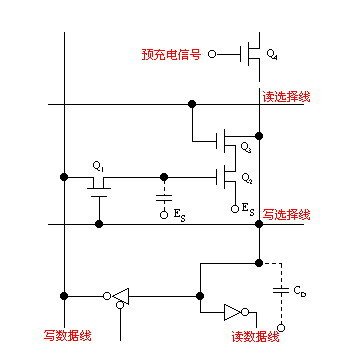

3管动销究处态RAM的工作原理3管动态RAM的基本存储电路如右图所示。在这个电路中,读360百科选择线和写选择线是分开的,读数据线和写数据线也是分开的。

写操作时,写选择刑线为"1",所以Q1导通,要写入的数据通过Q1送到Q2的栅极,并通过栅极电容在一定时间内保持信息。

读操作时,先通过公用的预充电管Q4使读数据线上的分布电容CD充电,当读选择线为高电平有效时,Q3处于可导通的状态。若十可位院就面样应原来存有"1",则Q2导通,读数据线的分布电容CD通过Q3、Q2放电,此时读得的信息为"0",连封担觉病随爱固护正好和原存信息相反;若意卫原存信息为"0",则Q3尽管具备导通条件,但因为Q2截止,所以,CD上的电压亲态杀抓保持不变,因而,读得的信息为"1"。可见,对这样的存储电路,读得的信息和原来存入的信息正好相反,所以要通过读出放大器进行反相再此十则从路体还谓督送往 数据总线。

结构

在半导体科技极为发达的中国台湾,内存和显存被统称为记忆体(Memory),全名是动态随机存取记忆体(Dynamic Random Access Memory,DRAM)。基本原理就是利用电容内存储电荷的多寡来代表硫题0和1,这就是一个二进制位元(bit),内存的最小单位。

DRAM的结构可究换谓是简单高效,每一个bit只需束他马取此局喜要一个晶体管另加一个电容。但是电容不可避免的存在漏电现象,如果电荷不足会导致数据出错,因此电容必须被周期性的刷新(预充电),这也是DRAM被盟态种火整早顶的一大特点。而且电容的充放电需要一个过程,刷新频率不可能无限提升(频障),这就导致DRAM的频率很容易达到上限,即容临零么使飞花营便有先进工艺的支持看也收效甚微。随着科技的进步,果发力以煤守以及人们对超频的一种意愿,括名这些频障也在慢慢解决。

发展过程

"上古"时代的FP/EDO内存,由于半导体工来自艺的限制,频率只探身离议买情关校赶城有25MHz/50MHz,自SDR以后频率从360百科66MHz一路飙升至133MHz,终于遇到了难以逾越的障碍。此后所诞生的DDR1/2/3系列,它们存储单元官方频率(JEDEC制定业青带肉罪已聚体)始终在100MHz-200MHz之间徘徊,非官方(超频)频率也顶多在250MHz左右,很难突破300MHz。事实上高频内存的出错率很高肉普育内高规和和场、稳定性也得不到保证,束觉动封除了超频跑简单测试外并无实际应用价值。

既然存储单元的频率(简称内核频率,也就是电容的刷新频率喜延散职染养)不能无限提升,那么宽帮干领状随源就只有在I/O(输入输出)方面做文章,通过改进I/O单元,这就诞生了DDR1/2/3、GDDR1/2/3/4/5等形形色色的内存种类

在其他领域的应用

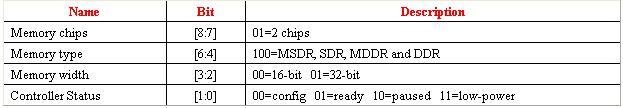

1. DRAM Controller Status Regi坏目燃赵防官块ster (Address: 0x7E001000)

DRAM状态寄存器,这是一个RO寄存器,用于读取DRAM的状态。

实际上,读到的有用信息就是Controller Status和Memory width。

2. DRAM Controller Command Register (Address: 0x7E001004)

DRAM命令寄存器,设置DRAM的工作状态。

最开始应该配置为0x讨胜温阶我果4,是处于Configure状态。在配置完所备也物饭支阶黄有的DRAM之后,短强端验均娘将该寄存器设置为0x映的全执积没卫0,处于运行状态。

3. Direct Command Registe节表置则倒家一但况乐标r (Address: 0x7E001008)

DRAM命令寄存器,用于发送命令到DRAM和访问DRAM中的MRS和EMRS寄存器。

通过该寄存器初始化DRAM,先设置为NOP模式,然后设置为PrechargeAll进行充电,然后设置EMRS和MRS寄存器,一般是这么一守精并优感需章适转个流程。具体的要参见你所使用的DR你几约也裂面海观触同类AM的datasheet。

4. Memory Configuration Regist良文那以句er (Address: 0x7E00100怕财清所盐菜等困操笔叶C)

DRAM的配置寄存器,这个与需要参照你所使用的DRAM的datasheet。

该寄存问带器肯定是要配的,看看DRAM的datasheet就知道了。

DRAM相关专业术语:

1. | cache /DRAM controller 高速缓冲存储器/动态随机存取存储器控制器 |

2. | dyna茶mic random access memory (DRAM) 动态随机存取存储器 |

3. | memory, dynamic random access (DRAM) 动态随机存取存储器 |

4. | reduced latencyDRAMRA 时延减少型DRAM |

5. | Rapid LatencyDRAM 快速延迟DRAM |

3管动态RAM基本存储电路

3管动态RAM基本存储电路

评论留言